# THÈSE

#### présentée à

### l'Université Paris 7 – Denis Diderot

*pour obtenir le titre de* **Docteur en Informatique**

## **A Shared Memory Poetics**

soutenue par

### JADE ALGLAVE

le 26 Novembre 2010

#### JURY

| Président    | Ahmed Bouajjani                   |

|--------------|-----------------------------------|

| Rapporteurs  | Gérard Boudol<br>Maurice Herlihy  |

| Examinateurs | Peter O'Hearn<br>Peter Sewell     |

| Directeurs   | Jean-Jacques Lévy<br>Luc Maranget |

## Contents

| Ι        | Pre       | eamble                                                                                  | 11              |

|----------|-----------|-----------------------------------------------------------------------------------------|-----------------|

| 1        | roduction | 13                                                                                      |                 |

|          | 1.1       | Context                                                                                 | 13              |

|          |           | 1.1.1 Early Days $(1979 - 1995)$                                                        | 13              |

|          |           | 1.1.2 Recent Days $(2002 - 2010)$                                                       | 19              |

|          | 1.2       | Contribution                                                                            | 20              |

|          |           | 1.2.1 A Generic Framework                                                               | 20              |

|          |           | 1.2.2 A Testing Tool                                                                    | 20              |

|          |           | 1.2.3 Synchronisation                                                                   | 21              |

|          |           | 1.2.4 Remainder $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 21              |

| <b>2</b> | Pre       | liminaries                                                                              | 23              |

| -        | 2.1       | Relations                                                                               | 23              |

|          |           | 2.1.1 Basic Definitions                                                                 | 23              |

|          |           | 2.1.2 Orders                                                                            | $\frac{-0}{24}$ |

|          | 2.2       | Linear Extension                                                                        | 25              |

|          | 2.3       | A Key Lemma                                                                             | 25              |

|          | -         | 2.3.1 Hexa Relation                                                                     | 26              |

|          |           | 2.3.2 Proof of the Result                                                               | 27              |

|          |           |                                                                                         |                 |

| II       | Α         | Generic Framework For Weak Memory Models                                                | 29              |

| 3        | AG        | Generic Framework                                                                       | 33              |

|          | 3.1       | Basic Objects                                                                           | 33              |

|          |           | 3.1.1 Events and Program Order                                                          | 35              |

|          | 3.2       | Execution Witnesses                                                                     | 35              |

|          |           | 3.2.1 Read-From Map                                                                     | 38              |

|          |           | 3.2.2 Write Serialisation                                                               | 38              |

|          |           | 3.2.3 From-Read Map                                                                     | 39              |

|          |           | 3.2.4 All Together                                                                      | 39              |

|          | 3.3       | Global Happens-Before                                                                   | 40              |

|          |           | 3.3.1 Globality $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 41              |

|    |                | 3.3.2 Preserved Program Order                     | 42 |

|----|----------------|---------------------------------------------------|----|

|    |                | 3.3.3 Barriers Constraints                        | 42 |

|    |                | 3.3.4 Architectures                               | 43 |

|    |                | 3.3.5 Examples                                    | 44 |

|    | 3.4            | Validity of an Execution                          | 45 |

|    |                | 3.4.1 Uniprocessor Behaviour                      | 45 |

|    |                | 3.4.2 Thin Air                                    | 48 |

|    |                | 3.4.3 Validity                                    | 49 |

|    | 3.5            | Comparing Architectures                           | 50 |

|    |                | 3.5.1 Validity Is Decreasing                      | 50 |

|    |                | 3.5.2 Monotonicity of Validity                    | 50 |

| 4  | Cla            | ssical Models                                     | 53 |

|    | 4.1            | Implementing an Architecture                      | 53 |

|    |                | 4.1.1 Building an Execution Witness From an Order | 54 |

|    |                | 4.1.2 Sketch of Proof                             | 57 |

|    | 4.2            | A Hierarchy of Classical Models                   | 59 |

|    |                | 4.2.1 Sequential Consistency (SC)                 | 60 |

|    |                | 4.2.2 The Sparc Hierarchy                         | 61 |

|    |                | 4.2.3 Alpha                                       | 65 |

|    |                | 4.2.4 RMO and Alpha Are Incomparable              | 67 |

| 5  | $\mathbf{Rel}$ | ated Work                                         | 71 |

|    | 5.1            | Generic Models                                    | 71 |

|    | 5.2            | Global-Time vs. View Orders                       | 72 |

|    | 5.3            | Axiomatic vs. Operational                         | 72 |

|    | 5.4            | Characterisation of Behaviours                    | 73 |

|    | 5.5            | Memory Models As Program Transformations          | 73 |

|    |                |                                                   |    |

| II | ΓΙ             | Cesting Weak Memory Models                        | 75 |

| 6  |                | axations                                          | 79 |

|    | 6.1            | A Brief Glance at the Power Documentation         | 79 |

|    |                | 6.1.1 Axioms of Our Model                         | 79 |

|    |                | 6.1.2 Store Buffering                             | 80 |

|    |                | 6.1.3 Load-Load Pairs                             | 81 |

|    |                | 6.1.4 Load-Store Pairs                            | 81 |

|    |                | 6.1.5 Barriers                                    | 82 |

|    | 6.2            | Candidate Relaxations                             | 85 |

|    |                | 6.2.1 Communication Candidate Relaxations         | 85 |

|    |                | 6.2.2 Program Order Candidate Relaxations         | 85 |

|    |                | 6.2.3 Barriers Candidate Relaxations              | 86 |

|    |                | 6.2.4 Dependencies Candidate Relaxations          | 87 |

|    |       | 6.2.5 Composite Candidate Relaxations                       | 88       |

|----|-------|-------------------------------------------------------------|----------|

|    | 6.3   | A Preliminary Power Model                                   | 89       |

| 7  | Div   | A Testing Tool                                              | 91       |

| •  | 7.1   | Litmus Tests                                                | 92       |

|    | 1.1   | 7.1.1 Highlighting Relaxations                              | 92<br>92 |

|    |       | 7.1.2 Exercising One Relaxation at a Time                   | 92       |

|    | 7.2   | Cycles as Specifications of Litmus Tests                    | 93       |

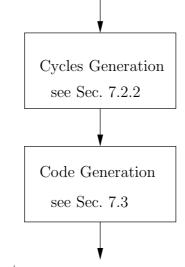

|    | 1.2   | 7.2.1 Automatic Test Generation                             | 93       |

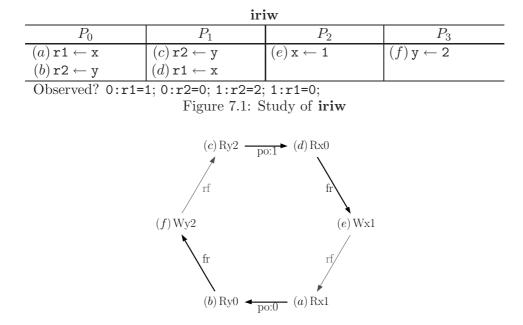

|    |       | 7.2.2 Cycles Generation                                     | 95       |

|    | 7.3   | Code Generation                                             | 96       |

|    | 1.0   | 7.3.1         Algorithm                                     | 96       |

|    |       | 7.3.2 Example                                               | 97       |

|    | 7.4   | A First Testing Example: x86-TSO                            | 98       |

|    |       | 7.4.1 A Guided Diy Run                                      | 99       |

|    |       | 7.4.2 Configuration Files                                   |          |

|    |       | 0                                                           |          |

| 8  | A F   |                                                             | 103      |

|    | 8.1   | The Phat Experiment                                         |          |

|    |       | 8.1.1 Relaxations Observed on squale, vargas and hpcx       |          |

|    |       | 8.1.2 Safe Relaxations                                      |          |

|    | 8.2   | Overview of Our Model                                       |          |

|    |       | 8.2.1 Additional Formalism                                  |          |

|    |       | 8.2.2 Description of the Model                              |          |

|    | 8.3   | Discussion of Our Model                                     | 118      |

| 9  | Rel   | ated Work                                                   | 121      |

| 0  | 1001  |                                                             |          |

|    |       |                                                             |          |

| IV | I S   | ynchronisation in Weak Memory Models                        | 123      |

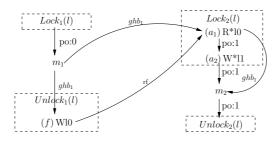

| 10 | ) Syn | chronisation                                                | 127      |

|    | v     | Covering and well-founded relations                         |          |

|    |       | 10.1.1 Covering relations                                   |          |

|    |       | 10.1.2 Well-founded relations                               |          |

|    | 10.2  | DRF guarantee                                               |          |

|    |       | 10.2.1 Competing accesses                                   |          |

|    |       | 10.2.2 Synchronising competing accesses in a weak execution |          |

|    |       |                                                             | 131      |

|    | 10.3  | Lock-free guarantee                                         |          |

|    |       | 10.3.1 Fragile pairs                                        |          |

|    |       | 10.3.2 Synchronising fragile pairs in a weak execution      |          |

|    |       | 10.3.3 Application to the Semantics of Barriers             |          |

|    |       | 10.3.4 Lock-free guarantee                                  |          |

| 10.4 Synchronisation idioms                                                                                 | 138 |

|-------------------------------------------------------------------------------------------------------------|-----|

| 10.4.1 Atomicity                                                                                            | 139 |

| 10.4.2 Locks                                                                                                | 139 |

| 10.4.3 Lock-free synchronisation                                                                            | 145 |

| 11 Stability                                                                                                | 149 |

| 11.1 Minimal cycles                                                                                         | 149 |

| 11.1.1 Violations $\ldots$ | 149 |

| 11.1.2 Covering the minimal violations                                                                      | 151 |

| 11.1.3 Critical cycles $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                       | 151 |

| 11.1.4 A characterisation of the minimal cycles $\ldots$ $\ldots$                                           | 154 |

| 11.2 Stability from any architecture to SC                                                                  | 155 |

| 12 Related Work                                                                                             | 159 |

| V Conclusion and Perspectives                                                                               | 163 |

| 13 Conclusion                                                                                               | 165 |

| 13.1 Divining Chicken Entrails                                                                              | 165 |

| 13.1.1 Reading the Documentations                                                                           |     |

| 13.1.2 Abstract Models                                                                                      | 166 |

| 13.1.3 Simple Formal Models                                                                                 | 166 |

| 13.1.4 The Preserved Program Order Quest                                                                    | 167 |

| 13.1.5 Strong Programming Disciplines                                                                       | 167 |

| 13.2 A Reading Frame For Weak Memory Models                                                                 |     |

| 13.2.1 A Common Prism $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                             | 168 |

| 13.2.2 Tests as Specifications                                                                              | 168 |

| 14 Perspectives                                                                                             | 169 |

| 14.1 Automatisation                                                                                         | 169 |

| 14.2 Formalisation of Diy                                                                                   | 169 |

| 14.3 Other Models And Paradigms                                                                             | 170 |

| 14.4 Testing Semantics For Weak Memory Models                                                               |     |

| 14.5 Logics For Weak Memory Models                                                                          |     |

| 14.6 Partial Orders As a Model of Concurrency                                                               | 172 |

| VI Appendix                                                                                                 | 181 |

| A Uniprocessor Equivalences                                                                                 | 183 |

| A.1 Some Handy Lemmas                                                                                       |     |

| A.2 $(Uni2)$ and $(Uni3)$ Are Equivalent                                                                    |     |

| A.3 $(Uni1)$ and $(Uni2)$ Are Equivalent                                                                    |     |

|                                                                                                             |     |

| В | AW  | Vord on the Coq Development          | 187 |

|---|-----|--------------------------------------|-----|

|   | B.1 | Overview of the Development          | 188 |

|   | B.2 | Basic Objects                        | 188 |

|   |     | B.2.1 Basic Types                    | 188 |

|   |     | B.2.2 Events and Program Order       | 190 |

|   |     | B.2.3 Execution Witnesses            | 192 |

|   | B.3 | Architectures and Weak Memory Models | 192 |

|   | B.4 | Proofs                               | 194 |

# Acknowledgements

Oh! I get by with a little help from my friends, Hmm, I get high with a little help from my friends, Hmm, I'm gonna try with a little help from my friends...

The Beatles—With a Little Help from My Friends [LM67c]

Ça vous occupera pendant que je fais le zouave au tableau! Et aussi, je ferai de bon cœur une dédicace manuscrite, ou je payerai une bière, à quiconque se sentirait floué de n'avoir pas été remercié ici.

Quand vous entendez ce petit tintement, tournez la page.

Pierre Clairambault · Jean-Baptiste Tristan · Delphine Longuet · Derek Williams · Xavier Leroy · Samuel Mimram · Fabrice Lemoine · Thomas Braibant · Paul-André Mellies

Ahmed Bouajjani • Amélie Mouton • Damien Doligez · Peter 0'Hearn · Vincent Jacques · Boris Yakobowski • Emmanuel Beffara • Florian Horn · Stéphane Zimmerman • Celtique · David Durrleman · Moscova · Marion Kermann · Gunther

Sikler · Proval · Contraintes · Julien Martin · Luc Maranget · Philippe Paul · David Baelde · Daniel Hirschkoff · Alexandre Buisse · Yann Strozecki · Aquinas Hobor · Nadia Mesrar · Julien Cristau · Peter Sewell · Brice Goglin · Nicolas Kornman · Sylvain Soliman · Arnaud Sangnier · Yves-Alexis Perez · Assia Mahboubi ·

Samuel Hym Boudol · • Gérard Florent Bouchy · Vincent Siles • Nicolas Guenot • Claire David · Sam Hocevar · Emmanuel Jeandel · Dider Rémy • Pierre Weis · Cédric Augonnet · Sandrine Blazy · Miles Alglave · Maurice Herlihy · Juliette Simonet · Johan Marcellan ·

Christian Gatore · Mexico · Runtime · Arthur Loiret · Étienne Lozes · Zaynah Dargaye · Roberto Di Cosmo · Thomas Lepoutre · Gallium · Pierre Habouzit · Cristiano Calcagno ·

Susmit Sarkar ·

Cyril Brulebois · Jules Villard ·

Vladimir

Katchadourian •

Jérémie Leymarie • Jean-Jacques Lévy • Samuel Thibault • Sylvain Schmitz • Sylvie Burini Part I Preamble

### Chapter 1

## Introduction

Roll up! Roll up for the magical mystery tour, step right this way!

The Beatles—Magical Mystery Tour [LM67a]

#### 1.1 Context

We give here a brief overview of the concepts that we will use throughout the manuscript. We illustrate these concepts with related work that we enjoyed reading, and that helped our comprehension of the vast area of weak memory models. This is nowhere near an exhaustive state of the art, but rather an overview of the work we found inspiring and from which our work inherits crucial ideas. We give in Fig. 1.1 a timeline of some of the related work we mention troughout the manuscript.

I guess that I had no idea how a program *should* behave. I may have been quite the only one; indeed programmers seem to expect certain behaviours and find others surprising when they run a program.

#### 1.1.1 Early Days (1979 - 1995)

#### 1.1.1.1 Sequential Consistency

Most of the time indeed, when writing a concurrent program, one expects (or would like) it to behave according to L. Lamport's *Sequential Consistency* (SC) [Lam79], where:

$[\ldots]$  the result of any execution is the same as if the operations of all the processors were executed in some sequential order, and the operations of each individual processor appear in this sequence in the order specified by its program.

|          | S. Adve and HJ. Boehm's position paper [AB]                                                                                    |

|----------|--------------------------------------------------------------------------------------------------------------------------------|

| 2010     | S. Burckhardt et al's study of program transformations [BMS]                                                                   |

| 2009     | PPC 2.06 [pow09]<br>Intel rev. 30 [int09]                                                                                      |

| 2008     | S. Adve and HJ. Boehm's C++ foundation [BA]<br>S. Burckhardt and M. Musuvathi's Efficient Enumeration Techniques for TSO [BMa] |

| 2007     | PPC 2.05 [ppc07] Intel White Paper [int07]<br>HJ. Boehm's Pthread's Locks study [Boea]                                         |

| 2006     | S. Burckhardt et al's Checkfence [BÅM]<br>Arvind and JW. Maessen's Instruction Reordering + Store Atomicity [AM]               |

| 2005     |                                                                                                                                |

|          | HJ. Boehm's Threads Cannot Be Implemented As A Library [Boeb]                                                                  |

| 2004     | S. Hangal et al's TSOTool [HVM <sup>+</sup> ]                                                                                  |

| 2003     | A. Adir et al's pre-cumulativity, view order style Power model [AAS03]                                                         |

| 2002     | Alpha's Fourth Edition [alp02]                                                                                                 |

|          |                                                                                                                                |

| 2000     |                                                                                                                                |

|          |                                                                                                                                |

|          |                                                                                                                                |

|          |                                                                                                                                |

|          | -                                                                                                                              |

|          | S. Adve and K. Gharachorloo's tutorial [AG95]                                                                                  |

| 1995     | K. Gharachorloo's thesis [Gha95]                                                                                               |

| 1994     | Sparc V9 [spa94b]                                                                                                              |

| 1993     | S. Adve's thesis (DRF) [Adv93]                                                                                                 |

| 1992     | W. Collier's framework[Col92]<br>Sparc V8 [spa92]                                                                              |

| 1991     | M. Herlihy's Wait-Free Synchronisation [Her]                                                                                   |

| 1990     | S. Adve and M. Hill's Weak Ordering [AH]                                                                                       |

|          | M. Dubois and C. Scheurich's Memory Access Dependencies In Shared-Memory Multiprocessors [DS90]                                |

| 1988     | D. Shasha and M. Snir's delay set algorithm [SS]                                                                               |

| 1987     |                                                                                                                                |

| 1301     | M. Dubois and C. Scheurich's Correct Memory Operation Of Cache Based Multiprocessors [SD87]                                    |

|          | -                                                                                                                              |

| 1985     | _                                                                                                                              |

|          |                                                                                                                                |

|          |                                                                                                                                |

|          | ]                                                                                                                              |

|          |                                                                                                                                |

| <u> </u> | -                                                                                                                              |

|          | [ Lemmant's $CO[1,, 70]$                                                                                                       |

| 1979     | L. Lamport's SC[Lam79]                                                                                                         |

Figure 1.1: Timeline of Selected Related Work

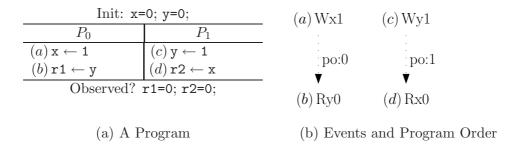

Consider for example the program given in Fig. 1.2(a), written in pseudo code. On  $P_0$ , we start with a store of value 1 to the memory location x, labelled (a), followed in program order by a load from memory location y into register **r1**, labelled (b). On  $P_1$ , we have a store of value 1 in memory location y, labelled (c), followed in program order by a load from memory location x into register **r2**, labelled (d). The registers are private to a processor, while the memory locations are shared.

We wonder whether the specified outcome—where r1 on  $P_0$  and r2 on  $P_1$  hold 0 in the end—can be observed if we assume SC as the execution model. The answer is no: SC authorises indeed only three final outcomes, depicted in Fig. 1.2(b). Suppose for example that the instructions on  $P_0$  are executed before the ones on  $P_1$ ; this corresponds to the first final state given in Fig. 1.2(b). In this case, the location x holds 1 because of the store (a) on  $P_0$ ; the load (b) reads the initial value of y, which is 0: hence r1 holds 0 in the end. Afterwards,  $P_1$  executes its instructions. The store (c) writes 1 into y, and the load (d) reads from the last store to x, which is (a). Since (a) wrote 1 into x, r2 holds 1 in the end.

#### 1.1.1.2 Weak Memory Models

However, for matters of performance, modern processors may provide features that induce behaviours a machine with a SC model would never exhibit, as L. Lamport already exposed in [Lam79]:

For some applications, achieving sequential consistency may not be worth the price of slowing down the processors. In this case, one must be aware that conventional methods for designing multiprocess algorithms cannot be relied upon to produce correctly executing programs.

Consider for example the test given in Fig. 1.2(c). It is the same test as in Fig. 1.2(a), but here it is written in x86 assembly. On  $P_0$ , the MOV [x], \$1 instruction corresponds to the store (a) of Fig. 1.2(a), and the MOV EAX, [y] corresponds to the load (b). Similarly on  $P_1$ , the MOV [y], \$1 instruction corresponds to the store (c), and the MOV EAX, [x] corresponds to the load (d). Although we expected only three possible outcomes when running this test, an x86 machine may exhibit the one which was specified in Fig. 1.2(a), because the store-load pairs on each processor may be reordered. Therefore, the load (b) on  $P_0$  may occur before the store (c) on  $P_1$ : in that case, the load (b) reads the initial value of y, which is 0. Similarly, the load (c) on  $P_1$  may occur before the store (a) on  $P_0$ , in which case (c) reads the initial value of x, which is 0. Thus, we obtain r1=0 and r2=0 as the final state.

Hence we cannot assume SC as the execution model of an x86 machine. A program running on a multiprocessor behaves w.r.t. the *memory model*

| Init: x=0; y=0;                        |                                                                                                                |  |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------|--|

| $P_0$                                  | $P_1$                                                                                                          |  |

| $(a) \mathtt{x} \leftarrow \mathtt{1}$ | $\begin{array}{c} (c)  \mathtt{y} \leftarrow \mathtt{1} \\ (d)  \mathtt{r2} \leftarrow \mathtt{x} \end{array}$ |  |

| $(b)\texttt{r1} \gets \texttt{y}$      | $(d)\mathtt{r2} \gets \mathtt{x}$                                                                              |  |

| Observed? r1=0; r2=0;                  |                                                                                                                |  |

(a) A Program

| (a) (b) (c) (d): $r1 = 0 \land r2 = 1$ |

|----------------------------------------|

| (c) (d) (a) (b): $r1 = 1 \land r2 = 0$ |

| (a) (c) (b) (d): $r1 = 1 \land r2 = 1$ |

(b) The Three SC Outcomes for this program

```

{0:EAX=0; 1:EAX=0;

x=0; y=0;}

P0 | P1 ;

MOV [x],$1 | MOV [y],$1 ;

MOV EAX,[y] | MOV EAX,[x] ;

exists (0:EAX=0 /\ 1:EAX=0)

Condition is validated

(c) This Program in x86 Assembly

```

Figure 1.2: An Example

of the architecture. The memory models we studied are said to be *weak*, or *relaxed w.r.t.* to SC, because they allow more behaviours than SC. For example, such models may allow *instruction reordering* [AG95, AM]: reads and writes may not be preserved in the program order, as we just saw with the example of Fig. 1.2(a). Some of them [ita02, pow09] also relax the *store atomicity* [AG95, AM] constraint. A write may not be available to all processors at once: it could be *e.g.* at first initiated by a given processor, then committed to a store buffer or a cache, and finally *globally performed* to memory [DS90], at which point only it will be available for all processors to see. Hence the value of a given write may be available to certain processors sooner than to others.

Therefore one needs to understand precisely the definition and consequences of a given memory model in order to predict the possible outcomes of a running program. But some public documentations [int07, pow09] lack formal definitions of these models. The effort of writing correct concurrent programs is increased by the absence of precise, if not formal, definitions.

#### 1.1.1.3 Synchronisation

SC is accepted as the most intuitive and simple memory model, as expressed *e.g.* by S. Adve and M. Hill in [AH]:

[...] programmers prefer to reason about sequentially consistent memory, rather than having to think about weaker memory, or even write buffers.

Hence, for easier reasoning, the key idea is to specify a "contract between software and hardware", such that [AH]:

$[\ldots]$  software agrees to some formally specified constraints, and hardware agrees to appear sequentially consistent to at least the software that obeys those constraints.

**Data Race Freeness Guarantee** As an example of such a contract, S. Adve and M. Hill proposed the Data Race Freeness Guarantee (DRF guarantee) [AH], ensuring a SC behaviour to a certain class of programs, the *correctly synchronised* [MPA] ones. They observe that [AH]:

The problem of maintaining sequential consistency manifests itself when two or more processors interact through memory operations on common variables.

For example, the test of Fig. 1.2(a) illustrates exactly the above statement: indeed it may exhibit a non-SC outcome, and involves two processors communicating *via* two shared memory locations x and y. So as to ensure that a program has a SC behaviour, S. Adve and M. Hill proposed the  $DRF_0$  model. The DRF guarantee states that if there is a mean to *arbitrate* the *data races* in a program, then this program can only have SC executions. We consider that two memory accesses from distinct processors form a data race when they both are relative to the same location and one of them at least is a write.

In the example of Fig. 1.2(a), the store (a) on  $P_0$  and the load (d) on  $P_1$  form a data race. They belong to distinct processors, are both relative to the memory location x, and (a) is a write. Symmetrically, the store (c) on  $P_1$  and the load (b) on  $P_0$  form a data race relative to the memory location y.

**Lock-Based Synchronisation** The most common way of using the DRF guarantee is *mutual exclusion locks*. Locks ensure a certain execution order on the accesses they protect, hence can be used to arbitrate conflicts [HS08]. Locks authorise access to a given protected memory location if and only if a certain flag (the lock) is free; otherwise, the processor willing to access the location has to wait for the lock to be released by the processor currently holding it.

Consider for example the test of Fig. 1.2(a), where the accesses (a) and (d)—relative to x—are protected by the same lock  $\ell$ , and the accesses (c) and (b)—relative to y—by another lock  $\ell'$ . This means that when the lock  $\ell$  is taken so that the access (a) is protected by  $\ell$ , the access (d) has to wait for the lock  $\ell$  to be free, and then to take it, to occur. The same reasoning applies for the accesses (c) and (b). The DRF guarantee ensures that the only possible outcomes of the modified program are the SC ones, given in Fig. 1.2(b).

However, locks suffer from several efficiency problems: they can induce some long delay of waiting for the lock to be free; see for example [HS08, 18.1.1, p.417].

**Lock-Free Synchronisation** In order to avoid the cost of locks, other synchronisation protocols were defined, such as *lock-free* synchronisation protocols. These protocols use synchronisation instructions provided by the architecture, such as *barriers* and composite synchronisation idioms, such as *test-and-set* or *compare-and-swap* [HS08, Sec. 5.6, p.112].

Consider for example the test of Fig. 1.2(a). Suppose that we place a barrier between (a) and (b) on  $P_0$ , and another one between (c) and (d) on  $P_1$ , such that these barriers prevent the reordering of write-read pairs. In this case, (a) and (b) cannot be reordered anymore; neither can (c) and (d). Therefore, the only possible outcomes of the modified program are the SC ones given in Fig. 1.2(b).

Contrarily to the DRF guarantee, lock-free protocols do not arbitrate data races. Thus they may improve the performance of the program. How-

ever, such a synchronisation requires a precise knowledge of the underlying memory model, since it uses barriers to prevent some weaknesses exhibited by the architecture. Thus the design and correctness of such protocols may be hard to prove, since the semantics of barriers is unclear, and the lack of formal definitions of weak memory models worsens the effort. The *delay set algorithm* by D. Shasha and M. Snir [SS] is an example of an early study of barriers placement, which assumes SC as the execution model.

#### 1.1.2 Recent Days (2002 - 2010)

Most of the concurrent verification work suppose SC as memory model, probably because multiprocessors were not mainstream until recently. Nowadays however, since multiprocessors are widely spread, there is a recrudescent interest in such issues. Indeed, as exposed by S. Adve and H.-J. Boehm in [AB]:

The problematic transformations (e.g. reordering accesses to unrelated variables  $[\ldots]$ ) never change the meaning of single-threaded programs, but do affect multithreaded programs  $[\ldots]$ .

#### 1.1.2.1 The Problem Of Modelling

Most of the existing formalised yet intelligible memory models are global time models, for example Alpha's [alp02] and Sparc's [spa94a]. In such models, the actions or events issued by the different threads or processors can be embedded in a single order, representing the timeline in which these events occurred w.r.t. the whole system. By this we mean that all the participants involved agree on that global ordering of the events. Hence I believe that such models are the easiest to understand and to reason with, which may explain their prominence.

Indeed weak memory models are a challenging area of modelling. Not only because they are intricated models, but also because most of the vendors do not provide an abstract model to reason about the architecture their machines exhibit, apart from a few rare exceptions [alp02, spa94a]. Moreover, as S. Adve and H.-J. Boehm state [AB]:

Part of the challenge for hardware architects was the lack of clear memory models at the programming language level—it was unclear what programmers expected hardware to do.

Thus modelling often resorts to intensive testing to support the theory. For example W. Collier's early work adopts a *black box testing* approach [Col92]. But this kind of approach is necessarily limited, and somewhat resembles wild guess, if it is not guided by a precise knowledge of either the architecture or the implementation.

#### 1.1.2.2 Program Verification

The interest in the area of weak memory models is also probably renewed by recent research [Boeb, Boea, BPa] that takes the intricacies of weak memory models into account when proposing a new approach to software verification. In particular, S. Adve and H.-J. Boehm lead a group dedicated to these issues: they propose to enforce the DRF guarantee as a *sine qua non* condition, so as to make the verification of concurrent programs easier. S. Burckhardt *et al.* recently proposed a study of weak memory models in terms of rewriting rules [BMS]: thus the weak memory model is itself a program transformation. This elegant approach allows to reason about the correctness of several program transformations, *e.g.* induced by compilers.

#### 1.2 Contribution

In that context, we tried to understand and formalise existing weak memory models. In order to do so, we first relied on the existing documentations. From this reading, we provided a generic framework which we showed to embrace several existing models. We then resorted to intensive testing to support our theory. To ease our pain while testing, we wrote a systematic testing tool, which computes small tests exercising one weakness of the architecture at a time. This allowed us to design a model for the Power architecture, which is an instance of our framework as well. Finally, we studied synchronisation in the context of weak memory models, whether lock-based or lock-free, from a generic point of view.

We briefly summarise our contribution here. We thus give an outline of the document, and some reading notes.

#### 1.2.1 A Generic Framework

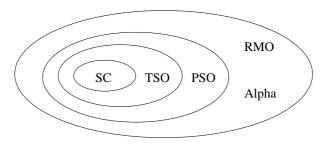

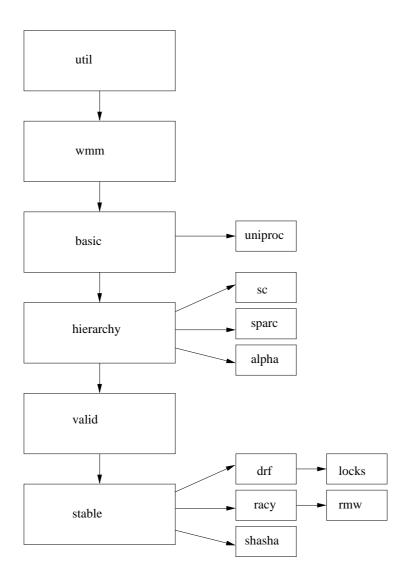

In Chap. 3, we present the generic axiomatic framework we developped in Coq [BC]. This is a global time model, widely inspired from Alpha and Sparc's documentation [alp02, spa94a]. We illustrate in Chap. 4 how to instantiate this framework to recover existing models, such as Sequential Consistency [Lam79], the Sparc hierarchy (*i.e.* Sun TSO, PSO and RMO) [spa94a], and Alpha [alp02]. We present some related work in Chap. 5, and detail some proofs in App. A.

Chap. 3 is the heart of this thesis, on which all our formal results are built. App. A can easily be skipped: the results which proofs are detailed in this chapter are described in Chap. 3 anyway.

#### 1.2.2 A Testing Tool

We present in Chap. 7 our div testing tool: div computes small tests in Power or x86 assembly code and run them against hardware. The tests are computed from specifications proceeding from our generic model, presented in Chap. 3. We present in Sec. 8.1 the way we used our tool to study the Power architecture. We detail our experimental protocol, the characteristics of the machines we tested and the experimental results. Finally in Chap. 8, we provide and comment on the model for the Power architecture we deduced from our experiments, and we present some related work in Chap. 9.

Chap. 8 is an interesting instance of our framework. The description of the tool (Chap. 7) and the detailed experimental protocol (Sec. 8.1) may be skipped as the description of the Power model is self-contained. However, the justification for this model lies in those two chapters, because this is where we explain how we build our tests, and why they are relevant.

#### 1.2.3 Synchronisation

We present in Chap. 11 a unifying approach to study both lock-based and lock-free synchronisations, which we illustrate by a proof that a generalised DRF guarantee holds for each instance of our generic model. We also provide a novel dual result on barrier placement. As both these results may enforce more synchronisation than necessary, we refine them in the style of D. Shasha and M. Snir [SS], by using *critical cycles*.

In addition, we present in Chap. 10 semantics for Power's locks and read-modify-write primitives. We show that these locks provide the refined generalised DRF guarantee. We show that the mapping of certain reads to read-modify-write primitives, coupled with non-cumulative barriers, restores Sequential Consistency, which spares the cost of cumulativity. Finally, we present some related work in Chap. 12.

#### 1.2.4 Remainder

Chap. 2 presents some preliminary definitions and fundamental results on relations and orders, which we use throughout the document. This chapter may be skipped.

We give a conclusion and some perspectives of future work in Chap. 13 and Chap. 14 respectively. We say a word on our Coq development in App. B, which may be skipped.

### Chapter 2

## Preliminaries

Our basic objects are *relations* over some elements. We give in this chapter the fundamental definitions that we used. We also enunciate and prove the key lemmas that we used.

#### 2.1 Relations

#### 2.1.1 Basic Definitions

We use homogeneous binary relations, that is we use relations  $\xrightarrow{r}$  such that r is, for a given set A, a set of pairs in  $A \times A$ .

We define the *domain* (written  $\operatorname{domain}(\stackrel{r}{\rightarrow})$ ) and the *range* ( $\operatorname{range}(\stackrel{r}{\rightarrow})$ ) of a relation  $\stackrel{r}{\rightarrow}$  as follows :

#### Definition 1 (Domain and Range of a Relation)

$$\begin{array}{rcl} \mathsf{domain}(\stackrel{r}{\rightarrow}) &\triangleq & \{x \mid \exists y, x \stackrel{r}{\rightarrow} y\} \\ \mathsf{range}(\stackrel{r}{\rightarrow}) &\triangleq & \{y \mid \exists x, x \stackrel{r}{\rightarrow} y\} \end{array}$$

We consider a relation  $\xrightarrow{r}$  to be *transitive* (written transitive( $\xrightarrow{r}$ )) when:

#### Definition 2 (Transitivity of a Relation)

$\mathsf{transitive}(\xrightarrow{\mathbf{r}}) \ \triangleq \ \forall xyz, (x \xrightarrow{\mathbf{r}} y \wedge y \xrightarrow{\mathbf{r}} z) \Rightarrow x \xrightarrow{\mathbf{r}} z$

We write  $\left(\stackrel{\mathbf{r}}{\rightarrow}\right)^+$  for the *transitive closure* of  $\stackrel{\mathbf{r}}{\rightarrow}$ , that is:

#### Definition 3 (Transitive Closure of a Relation)

$x\left(\stackrel{\mathrm{r}}{\rightarrow}\right)^{+}y \ \triangleq \ x \stackrel{\mathrm{r}}{\rightarrow} y \lor \left(\exists z, x\left(\stackrel{\mathrm{r}}{\rightarrow}\right)^{+}z \land z\left(\stackrel{\mathrm{r}}{\rightarrow}\right)^{+}y\right)$

We consider a relation  $\xrightarrow{r}$  to be *irreflexive* (written irreflexive( $\xrightarrow{r}$ )) when:

Definition 4 (Irreflexivity of a Relation)

$$\mathsf{irreflexive}(\overset{\mathbf{r}}{\rightarrow}) \ \triangleq \ \neg(\exists x, x \overset{\mathbf{r}}{\rightarrow} x)$$

We consider a relation  $\xrightarrow{r}$  to be *total* over a set  $\mathbb{E}$  (written  $total(\xrightarrow{r}, \mathbb{E})$ ) when:

#### Definition 5 (Totality of a Relation)

$$\mathsf{total}(\stackrel{\mathrm{r}}{\to}, \mathbb{E}) \triangleq \forall (x, y) \in \mathbb{E} \times \mathbb{E}, x \stackrel{\mathrm{r}}{\to} y \lor y \stackrel{\mathrm{r}}{\to} x$$

We consider a relation  $\xrightarrow{\mathbf{r}}$  to be *acyclic* (written  $\operatorname{acyclic}(\xrightarrow{\mathbf{r}})$ ) when its transitive closure is irreflexive, *i.e.*:

#### Definition 6 (Acyclicity of a Relation)

$$\operatorname{acyclic}(\stackrel{\mathrm{r}}{\to}) \triangleq \neg(\exists x, x (\stackrel{\mathrm{r}}{\to})^+ x)$$

#### 2.1.2 Orders

We consider a relation  $\xrightarrow{\mathbf{r}}$  to be a *partial order* over a set  $\mathbb{E}$  when:

- the domain and the range of  $\xrightarrow{r}$  are included in  $\mathbb{E}$ ,

- $\xrightarrow{r}$  is transitive, and

- $\xrightarrow{r}$  is irreflexive.

Formally, we have:

#### Definition 7 (Partial Order)

$\begin{array}{ll} \mathsf{partial-order}(\stackrel{r}{\to},\mathbb{E}) &\triangleq & (\mathsf{domain}(\stackrel{r}{\to}) \cup \mathsf{range}(\stackrel{r}{\to})) \subseteq \mathbb{E} \land \\ & \mathsf{transitive}(\stackrel{r}{\to}) \land \mathsf{irreflexive}(\stackrel{r}{\to}) \end{array}$

We consider a relation  $\xrightarrow{r}$  to be a *total order* (or *linear strict order*) over  $\mathbb{E}$  when:

- $\xrightarrow{r}$  is a partial order over  $\mathbb{E}$ , and

- $\stackrel{\mathrm{r}}{\rightarrow}$  is total over  $\mathbb{E}$ .

Formally, we have:

#### Definition 8 (Total Order)

$\mathsf{total}\text{-}\mathsf{order}(\overset{r}{\rightarrow},\mathbb{E}) \ \triangleq \ \mathsf{partial}\text{-}\mathsf{order}(\overset{r}{\rightarrow},\mathbb{E}) \land \mathsf{total}(\overset{r}{\rightarrow},\mathbb{E})$

#### 2.2 Linear Extension

We admit the following result: any partial order  $\xrightarrow{r}$  can be *extended* into a total order  $\xrightarrow{o}$ . This total order  $\xrightarrow{o}$  is a *linear extension* of  $\xrightarrow{r}$ . We write linear-extension( $\xrightarrow{o}$ ,  $\xrightarrow{r}$ ) to indicate that  $\xrightarrow{o}$  is a linear extension of  $\xrightarrow{r}$ . Formally, we have:

#### Axiom 1 (Existence of a Linear Extension)

$\begin{array}{c} \forall \stackrel{r}{\rightarrow} \mathbb{E}, \mathsf{partial-order}(\stackrel{r}{\rightarrow}, \mathbb{E}) \Rightarrow \\ \exists \stackrel{o}{\rightarrow}, \mathsf{linear-extension}(\stackrel{o}{\rightarrow}, \stackrel{r}{\rightarrow}) \land \mathsf{total-order}(\stackrel{o}{\rightarrow}, \mathbb{E}) \end{array}$

We admit that a relation  $\xrightarrow{r}$  is included in any of its linear extension:

#### Axiom 2 (Inclusion in its Linear Extensions)

$\forall \xrightarrow{r} \overset{o}{\to}, \mathsf{linear-extension}(\xrightarrow{o}, \xrightarrow{r}) \Rightarrow (\xrightarrow{r} \subseteq \xrightarrow{o})$

Finally, when  $\xrightarrow{r}$  is already a total order,  $\xrightarrow{r}$  has only one linear extension, which is itself:

Axiom 3 (Unicity of the Linear Extension of a Total Order)

$\forall \stackrel{r}{\rightarrow} \mathbb{E}, \mathsf{total-order}(\stackrel{r}{\rightarrow}, \mathbb{E}) \Rightarrow (\forall \stackrel{o}{\rightarrow}, \mathsf{linear-extension}(\stackrel{o}{\rightarrow}, \stackrel{r}{\rightarrow}) \Rightarrow \stackrel{o}{\rightarrow} = \stackrel{r}{\rightarrow})$

#### 2.3 A Key Lemma

We define the sequence of two relations  $\xrightarrow{r_1}$  and  $\xrightarrow{r_2}$  (written  $(\xrightarrow{r_1}; \xrightarrow{r_2})$ ) as follows:

#### Definition 9 (Sequence of Relations)

$$x(\stackrel{\mathbf{r}_1}{\rightarrow};\stackrel{\mathbf{r}_2}{\rightarrow})y \triangleq \exists z, x \stackrel{\mathbf{r}_1}{\rightarrow} z \land z \stackrel{\mathbf{r}_2}{\rightarrow} y$$

We will often show that the acyclicity of a certain relation  $\xrightarrow{r_1}$  implies the acyclicity of another one  $\xrightarrow{r_2}$ . In order to do so, we reason by contradiction: we suppose that  $\xrightarrow{r_2}$  has a cycle, and show that in this case,  $\xrightarrow{r_1}$  has a cycle as well, which contradicts its acyclicity.

In order to prove this, we use this key lemma, which states that if there is a cycle in the union of two irreflexive relations, there is a cycle in their sequence as well:

#### Lemma 1 (Cycle in Union Implies Cycle in Sequence)

$$\begin{array}{c} \forall \stackrel{r_1}{\to} \stackrel{r_2}{\to}, \text{irreflexive}(\stackrel{r_1}{\to}) \land \text{irreflexive}(\stackrel{r_2}{\to}) \land \\ \text{transitive}(\stackrel{r_1}{\to}) \land \text{transitive}(\stackrel{r_2}{\to}) \land \\ \neg(\text{acyclic}(\stackrel{r_1}{\to} \cup \stackrel{r_2}{\to})) \Rightarrow \neg(\text{acyclic}(\stackrel{r_1}{\to}; \stackrel{r_2}{\to})) \end{array}$$

We need to establish a few more lemmas to prove this result.

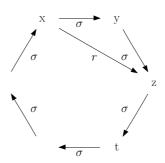

#### 2.3.1 Hexa Relation

We define the reflexive closure over relations as follows:

Definition 10 (Reflexive Closure)

$$x \left(\stackrel{\mathbf{r}}{\rightarrow}\right)^? y \triangleq x \stackrel{\mathbf{r}}{\rightarrow} y \lor x = y$$

This means that two elements x and y are in  $(\stackrel{\mathbf{r}}{\rightarrow})^{?}$  when they are in  $\stackrel{\mathbf{r}}{\rightarrow}$  or x = y. Note that for any relation  $\stackrel{\mathbf{r}}{\rightarrow}$  and for all x, we have  $x (\stackrel{\mathbf{r}}{\rightarrow})^{?} x$ .

We define the binary operator phx over relations as follows:

#### Definition 11 (Pre Hexa)

$$\mathsf{phx}(\xrightarrow{r_1}, \xrightarrow{r_2}) \triangleq ((\xrightarrow{r_1}; \xrightarrow{r_2})^+)?$$

Note that, since phx is a reflexive closure, we have  $(x, x) \in phx(\xrightarrow{r_1}, \xrightarrow{r_2})$  for all  $\xrightarrow{r_1}$ ,  $\xrightarrow{r_2}$  and x. Moreover, a phx construction is trivially transitive.

We define the binary operator hx over relations as follows:

#### Definition 12 (Hexa)

$$\mathsf{hx}(\stackrel{\mathrm{r}_1}{\to},\stackrel{\mathrm{r}_2}{\to}) \triangleq (\stackrel{\mathrm{r}_2}{\to})^?; \mathsf{phx}(\stackrel{\mathrm{r}_1}{\to},\stackrel{\mathrm{r}_2}{\to}); (\stackrel{\mathrm{r}_1}{\to})^?$$

We show that the hx of two transitive relations is a transitive relation:

#### Lemma 2 (Hexa Is Transitive)

$\forall \xrightarrow{r_1 r_2}, \mathsf{transitive}(\xrightarrow{r_1}) \land \mathsf{transitive}(\xrightarrow{r_2}) \Rightarrow \mathsf{transitive}(\mathsf{hx}(\xrightarrow{r_1}, \xrightarrow{r_2}))$

**Proof** Suppose x, y and z such that  $(x, y) \in hx(\xrightarrow{r_1}, \xrightarrow{r_2})$  and  $(y, z) \in hx(\xrightarrow{r_1}, \xrightarrow{r_2})$ . There exist  $z_1, z_2, z_3$  and  $z_4$  such that

$$x\left(\stackrel{r_{2}}{\rightarrow}\right)^{?} z_{1} \operatorname{phx}\left(\stackrel{r_{1}}{\rightarrow}, \stackrel{r_{2}}{\rightarrow}\right) z_{2}\left(\stackrel{r_{1}}{\rightarrow}\right)^{?} y\left(\stackrel{r_{2}}{\rightarrow}\right)^{?} z_{3} \operatorname{phx}\left(\stackrel{r_{1}}{\rightarrow}, \stackrel{r_{2}}{\rightarrow}\right) z_{4}\left(\stackrel{r_{1}}{\rightarrow}\right)^{?} z_{4}\left(\stackrel{r_{2}}{\rightarrow}\right)^{?} z_{5}\left(\stackrel{r_{2}}{\rightarrow}\right)^{?} z_{5}\left(\stackrel{r_{2}}{\rightarrow}\right)$$

We have  $z_2(\stackrel{r_1}{\rightarrow})^? y(\stackrel{r_2}{\rightarrow})^? z_3$ , hence  $(z_2, z_3) \in \mathsf{phx}(\stackrel{r_1}{\rightarrow}, \stackrel{r_2}{\rightarrow})$ . Since a phx construction is transitive, we have  $(z_1, z_4) \in \mathsf{phx}(\stackrel{r_1}{\rightarrow}, \stackrel{r_2}{\rightarrow})$ , hence  $x(\stackrel{r_2}{\rightarrow})^? z_1 \mathsf{phx}(\stackrel{r_1}{\rightarrow}, \stackrel{r_2}{\rightarrow})$  $)z_4(\stackrel{r_1}{\rightarrow})^? z$ . Therefore, by the definition of hx, we have  $(x, z) \in \mathsf{hx}(\stackrel{r_1}{\rightarrow}, \stackrel{r_2}{\rightarrow})$ . We show that when two relations  $\stackrel{r_1}{\rightarrow}$  and  $\stackrel{r_2}{\rightarrow}$  are both transitive, a path

We show that when two relations  $\xrightarrow{r_1}$  and  $\xrightarrow{r_2}$  are both transitive, a path in their union is a path in  $hx(\xrightarrow{r_2}, \xrightarrow{r_1})$ :

#### Lemma 3 (Path in Union Implies Path in Hexa)

$\forall \xrightarrow{r_1 r_2}, \mathsf{transitive}(\xrightarrow{r_1}) \land \mathsf{transitive}(\xrightarrow{r_2}) \Rightarrow ((\xrightarrow{r_1} \cup \xrightarrow{r_2})^+ \subseteq \mathsf{hx}(\xrightarrow{r_2}, \xrightarrow{r_1}))$

**Proof** Suppose x and y such that  $x (\xrightarrow{r_1} \cup \xrightarrow{r_2})^+ y$ . Let us reason by induction over this statement.

• Suppose  $x(\xrightarrow{r_1} \cup \xrightarrow{r_2})y$ .

- Suppose  $x \xrightarrow{r_1} y$ . We want to show that  $(x, y) \in \mathsf{hx}(\xrightarrow{r_2}, \xrightarrow{r_1})$ , i.e. there exist  $z_1$  and  $z_2$  such that  $x(\xrightarrow{r_1})^? z_1 \mathsf{phx}(\xrightarrow{r_2}, \xrightarrow{r_1}) z_2(\xrightarrow{r_2})^? y$ . We know that  $x(\xrightarrow{r_1})^? y$  since  $x \xrightarrow{r_1} y$ . Hence we can take  $z_1 = y$ . Since  $(y, y) \in \mathsf{phx}(\xrightarrow{r_2}, \xrightarrow{r_1})$ , we can take  $z_2 = y$ . Indeed we have  $y(\xrightarrow{r_2})^? y$ .

- Suppose  $x \xrightarrow{r_2} y$ , we can take  $z_1 = z_2 = x$ .

In the inductive case, we have z such that x hx(<sup>r<sub>2</sub></sup>→, <sup>r<sub>1</sub></sup>→)z and z hx(<sup>+</sup>→, <sup>+</sup>→)y. By Lem. 2, we have the result.

We show that if  $(\stackrel{r_2}{\rightarrow}; \stackrel{r_1}{\rightarrow})$  is acyclic, then  $(hx(\stackrel{r_2}{\rightarrow}, \stackrel{r_1}{\rightarrow}); \stackrel{r_1}{\rightarrow})$  is irreflexive, provided  $\stackrel{r_1}{\rightarrow}$  is irreflexive and transitive:

#### Lemma 4 (Hexa Right)

$$\begin{array}{l} \forall \xrightarrow{\mathbf{r}_1 \mathbf{r}_2} xy, \mathsf{irreflexive}(\xrightarrow{\mathbf{r}_1}) \land \mathsf{transitive}(\xrightarrow{\mathbf{r}_1}) \land \\ (x,y) \in \mathsf{hx}(\xrightarrow{\mathbf{r}_2}, \xrightarrow{\mathbf{r}_1}) \land y \xrightarrow{\mathbf{r}_1} x \Rightarrow \exists z, z \left(\xrightarrow{\mathbf{r}_2}; \xrightarrow{\mathbf{r}_1}\right)^+ z \end{array}$$

**Proof** Suppose x and y such that  $(x, y) \in hx(\stackrel{r_2}{\to}, \stackrel{r_1}{\to})$  and  $y \stackrel{r_1}{\to} x$ . There are  $z_1$  and  $z_2$  such that  $x(\stackrel{r_1}{\to})^? z_1 phx(\stackrel{r_2}{\to}, \stackrel{r_1}{\to}) z_2(\stackrel{r_2}{\to})^? y$ . The case when x = y is a direct contradiction to the fact that  $\stackrel{r_1}{\to}$  is irreflexive, since  $y \stackrel{r_1}{\to} x$  by hypothesis. Otherwise, we have  $z_1(\stackrel{r_2}{\to}; \stackrel{r_1}{\to})^+ z_1$ .

We show that if  $(\stackrel{r_2}{\rightarrow}; \stackrel{r_1}{\rightarrow})$  is acyclic, then  $(\stackrel{r_1}{\rightarrow}; hx(\stackrel{r_2}{\rightarrow}, \stackrel{r_1}{\rightarrow}))$  is irreflexive, provided  $\stackrel{r_2}{\rightarrow}$  is irreflexive and transitive:

#### Lemma 5 (Hexa Left)

$$\forall \stackrel{\mathbf{r}_1}{\to} \stackrel{\mathbf{r}_2}{\to} xy, \text{irreflexive}(\stackrel{\mathbf{r}_2}{\to}) \land \text{transitive}(\stackrel{\mathbf{r}_2}{\to}) \land \\ x \stackrel{\mathbf{r}_2}{\to} y \land (y, x) \in \mathsf{hx}(\stackrel{\mathbf{r}_2}{\to}, \stackrel{\mathbf{r}_1}{\to}) \Rightarrow \exists z, z (\stackrel{\mathbf{r}_2}{\to}; \stackrel{\mathbf{r}_1}{\to})^+ z$$

**Proof** The proof is similar to the proof of Lem. 4 above.

#### 2.3.2 Proof of the Result

We want to prove the Lem. 1:

$$\begin{array}{c} \forall \xrightarrow{r_1 r_2}, \mathsf{irreflexive}(\xrightarrow{r_1}) \land \mathsf{irreflexive}(\xrightarrow{r_2}) \land \\ \mathsf{transitive}(\xrightarrow{r_1}) \land \mathsf{transitive}(\xrightarrow{r_2}) \land \\ \neg(\mathsf{acyclic}(\xrightarrow{r_1} \cup \xrightarrow{r_2})) \Rightarrow \neg(\mathsf{acyclic}(\xrightarrow{r_1}; \xrightarrow{r_2})) \end{array}$$

**Proof** Since  $\neg (\operatorname{acyclic}(\stackrel{r_1}{\to} \cup \stackrel{r_2}{\to}))$ , there is x such that  $x (\stackrel{r_1}{\to} \cup \stackrel{r_2}{\to})^+ x$ . Therefore, there is z such that  $x (\stackrel{r_1}{\to} \cup \stackrel{r_2}{\to}) z$  and  $(z (\stackrel{r_1}{\to} \cup \stackrel{r_2}{\to})^+ x) \lor (x = z)$ . We do a case disjunction over this last statement.

• Suppose x = z. As  $x(\stackrel{r_1}{\to} \cup \stackrel{r_2}{\to})z$ , we have  $x(\stackrel{r_1}{\to} \cup \stackrel{r_2}{\to})x$ . But since  $\stackrel{r_1}{\to}$  and  $\stackrel{r_2}{\to}$  are both irreflexive, their union is irreflexive as well, hence the result.

• Suppose  $(z(\stackrel{r_1}{\rightarrow}\cup\stackrel{r_2}{\rightarrow})^+x)$ . In this case, we have  $(z((\stackrel{r_1}{\rightarrow})^+\cup(\stackrel{r_2}{\rightarrow})^+)^+x)$ . By Lem. 3, we have  $(z,x) \in hx((\stackrel{r_2}{\rightarrow})^+,(\stackrel{r_1}{\rightarrow})^+)$ .

Moreover, we know that  $x(\stackrel{r_1}{\rightarrow} \cup \stackrel{r_2}{\rightarrow})z$ . Let us do a case disjunction over this statement.

- Suppose  $x \stackrel{r_1}{\to} z$ . By Lem. 4 applied to  $(z, x) \in hx((\stackrel{r_2}{\to})^+, (\stackrel{r_1}{\to})^+)$  and  $x \stackrel{r_1}{\to} z$ , we have the result.

- Suppose now  $x \xrightarrow{r_2} z$ . By Lem. 5 applied to  $x \xrightarrow{r_2} z$  and  $(z,x) \in hx((\xrightarrow{r_2})^+, (\xrightarrow{r_1})^+)$ , we have the result.

## Part II

# A Generic Framework For Weak Memory Models

We present here a generic framework designed to reason on weak memory models. Though some public documentations, e.g. Intel [int07] and Power [pow09], lack formal definitions of these models, others—such as Alpha [alp02] and Sparc [spa94a]—provide a precise definition of the model their processors exhibit. Our generic framework is widely inspired of the common style of Alpha and Sparc's documentations, in that we use a global time axiomatic model. However, Alpha and Sparc consider the stores to be atomic. We adapted the style of their model to allow the store atomicity relaxation, as does e.g. Power. In addition, we took care to minimise the number and the complexity of our axioms, so that they are easier to understand.

We present in Chap. 3 the objects, terms and axioms of our framework. We illustrate in Chap. 4 how to instantiate its parameters to produce several well known models, namely *Sequential Consistency* [Lam79], the Sparc hierarchy (*i.e.* TSO, PSO and RMO) [spa94a], and Alpha [alp02]. We conclude with a presentation of some related work in Chap. 5.

### Chapter 3

### **A Generic Framework**

#### 3.1 Basic Objects

A memory model determines whether a candidate execution of a program is *valid*. We consider an execution of a given program to be valid when the read and write memory events associated with the instructions of the program follow a single global timeline, *i.e.* can be embedded in a single partial order. This order represents the timeline in which these events are *globally performed*, which means that we embed them in the order when we reach the point in time where all processors involved have to take these events into account.

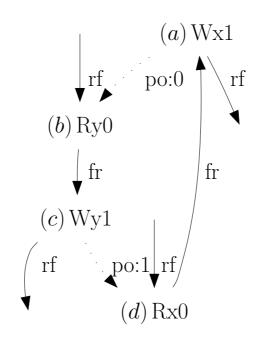

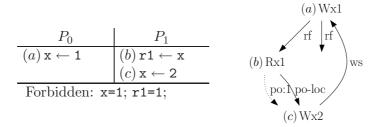

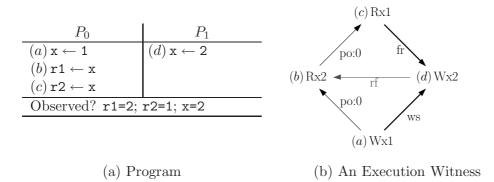

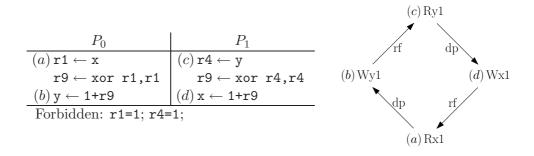

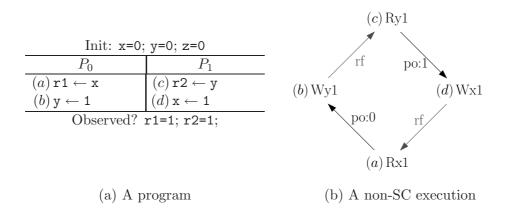

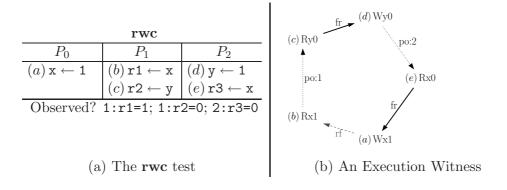

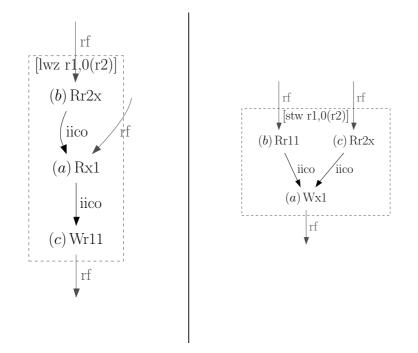

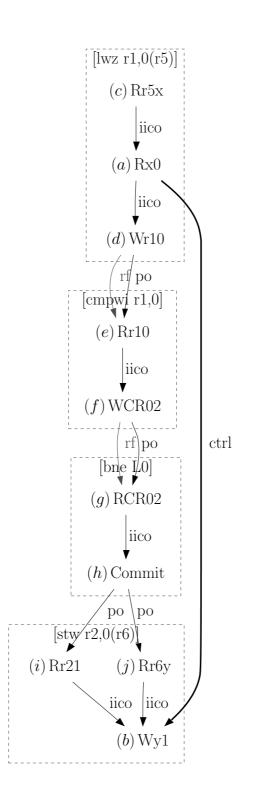

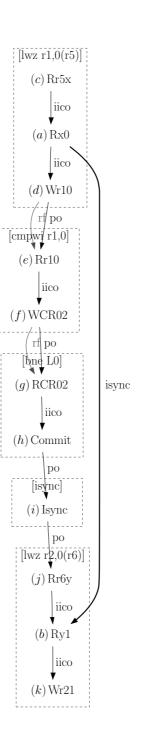

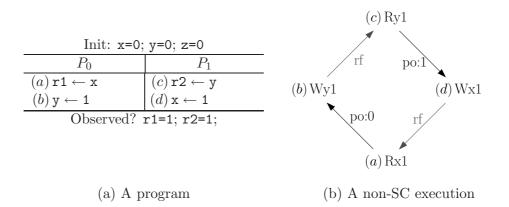

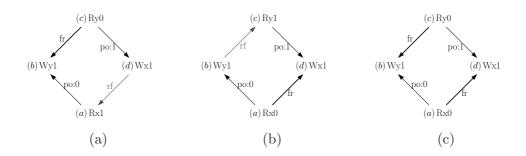

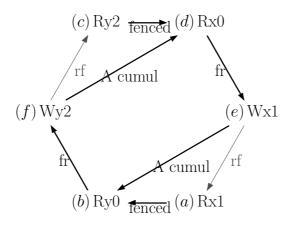

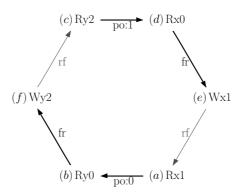

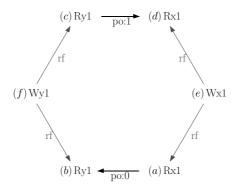

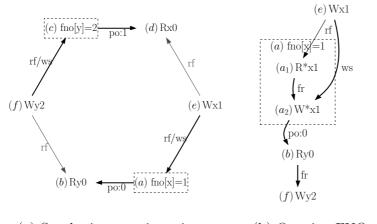

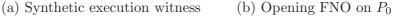

We illustrate our model with *litmus* tests, which are simple tests in pseudo- or assembly code. Fig. 3.1(a) shows such a test, with an initial state (which gathers the initial values of registers and memory locations used in the test), a program in pseudo- or assembly code, and a final condition on registers and memory (we write x, y for memory locations and r1, r2 for registers). We give in Fig. 3.1(b) an execution associated with this test. The validity of this execution is relative to the architecture on which it runs: it is valid on an architecture such as x86, whereas it is invalid on SC.

Figure 3.1: A Program and an Event Structure

Figure 3.2: An Execution for the Program of Fig. 3.1

#### 3.1.1 Events and Program Order

Rather than dealing directly with programs, our models are expressed in terms of the *events*  $\mathbb{E}$  occurring in a candidate execution. A *memory event* m represents a memory access, specified by its direction (write or read), its location  $\mathsf{loc}(m)$ , its processor  $\mathsf{proc}(m)$ , and a unique label. For example, the store to x marked (a) in Fig. 3.1(a) generates the event (a) Wx in Fig. 3.1(b). Henceforth, we write r (resp. w) for a read (resp. write) event. We write  $\mathbb{M}_{\ell}$  (resp.  $\mathbb{R}_{\ell}, \mathbb{W}_{\ell}$ ) for the set of memory events (resp. reads, writes) to a location  $\ell$  (we omit  $\ell$  when quantifying over all of them). We give a table of notations for these sets of events, and the corresponding cartesian products in Fig. 3.4.

The models are defined in terms of binary relations over these events, and Fig. 3.3 shows a table of the relations we use.

The program order  $\stackrel{\text{po}}{\rightarrow}$  is a total order amongst the events from the same processor that never relates events from different processors. It reflects the sequential execution of instructions on a single processor: given two instruction execution instances  $i_1$  and  $i_2$  that generate events  $e_1$  and  $e_2$ ,  $e_1 \stackrel{\text{po}}{\rightarrow} e_2$  means that a sequential processor would execute  $i_1$  before  $i_2$ . When instructions may perform several memory accesses, we take intra-instruction dependencies [SSZN<sup>+</sup>] into account to build a more precise order.

Hence we describe a program by an *event structure*, which collects the memory events issued by the instructions of this program, and the program order relation, which lifts the program order between instructions to the events' level:

#### Definition 13 (Event Structure)

$$E \triangleq (\mathbb{E}, \stackrel{\mathrm{po}}{\rightarrow})$$

Consider for example the test given in Fig. 3.1(a). We give in Fig. 3.1(b) an associated event structure. For example, to the store instruction marked (a) on  $P_0$ , we associate the write event (a) Wx in Fig. 3.1(b). To the load instruction marked (b) on  $P_0$ , we associate the read event (b) Ry in Fig. 3.1(b). Since these two instructions are in program order on  $P_0$ , the associated events are related by the  $\stackrel{\text{po}}{\rightarrow}$  relation. The reasoning is similar on  $P_1$ .

#### 3.2 Execution Witnesses

Although  $\xrightarrow{\text{po}}$  conveys important features of program execution, *e.g.* branch resolution, it does not characterise an execution. Indeed, on a weak memory model, the events in program order may be reordered in an execution. Moreover, we need to describe the communication between distinct processors during the execution of a program. Hence, in order to describe an execution, we postulate two relations  $\xrightarrow{\text{rf}}$  and  $\xrightarrow{\text{ws}}$  over memory events.

| Name                    | Notation                                | Comment                                                                                                                 | Sec.    |

|-------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------|

| program order           | $m_1 \xrightarrow{\text{po}} m_2$       | per-processor total order                                                                                               | 3.1.1   |

| dependencies            | $m_1 \xrightarrow{\mathrm{dp}} m_2$     | included in $\xrightarrow{\text{po}}$ , source is a read                                                                | 3.4.1.3 |

| po-loc                  | $m_1 \stackrel{\text{po-loc}}{\to} m_2$ | program order restricted to the same location, included in $\xrightarrow{\text{po}}$                                    | 3.4.1.1 |

| preserved program order | $m_1 \xrightarrow{\text{ppo}} m_2$      | pairs maintained in program order, included in $\xrightarrow{\text{po}}$                                                | 3.3.2   |

| read-from map           | $w \xrightarrow{\mathrm{rf}} r$         | links a write to a read reading its value                                                                               | 3.2.1   |

| external read-from map  | $w \xrightarrow{\mathrm{rfe}} r$        | $\xrightarrow{\mathrm{rf}}$ between events from distinct pro-                                                           | 3.3.1   |

|                         |                                         | cessors                                                                                                                 |         |

| internal read-from map  | $w \xrightarrow{\mathrm{rfi}} r$        | $\xrightarrow{\mathrm{rf}}$ between events from the same pro-                                                           | 3.3.1   |

|                         |                                         | cessor                                                                                                                  |         |

| global read-from map    | $w \xrightarrow{\operatorname{grf}} r$  | $\stackrel{\rm rf}{\rightarrow}$ considered global                                                                      | 3.3.1   |

| write serialisation     | $w_1 \xrightarrow{\mathrm{ws}} w_2$     | total order on writes to the same lo-                                                                                   | 3.2.2   |

|                         |                                         | cation                                                                                                                  |         |

| from-read map           | $r \xrightarrow{\text{fr}} w$           | $r$ reads from a write preceding $w$ in $\stackrel{\rm ws}{\rightarrow}$                                                | 3.2.3   |

| barriers                | $m_1 \xrightarrow{\mathrm{ab}} m_2$     | ordering induced by barriers                                                                                            | 3.3.3   |

| global happens-before   | $m_1 \stackrel{\text{ghb}}{\to} m_2$    | union of global relations                                                                                               | 3.3.4   |

| communication           | $m_1 \stackrel{\text{com}}{\to} m_2$    | shorthand for $m_1 (\stackrel{\mathrm{rf}}{\to} \cup \stackrel{\mathrm{ws}}{\to} \cup \stackrel{\mathrm{fr}}{\to}) m_2$ | 3.2.4   |

Figure 3.3: Table of Relations

| Name                                   | Notation                                     | Comment                                                               |  |

|----------------------------------------|----------------------------------------------|-----------------------------------------------------------------------|--|

| memory events                          | $\mathbb{M}$                                 | all memory events                                                     |  |

| memory events to the same location     | $\mathbb{M}_{\ell}$                          | memory events relative to the location $\ell$                         |  |

| read events, reads                     | $\mathbb{R}$                                 | memory events that are reads                                          |  |

| reads from the same location           | $\mathbb{R}_{\ell}$                          | reads from the location $\ell$                                        |  |

| write events, writes                   | W                                            | memory events that are writes                                         |  |

| writes to the same location            | $\mathbb{W}_{\ell}$                          | writes to the location $\ell$                                         |  |

| memory pairs                           | $\mathbb{M}\times\mathbb{M}$                 | pairs of any memory events in program order                           |  |

| memory pairs to the same location      | $\mathbb{M}_{\ell} \times \mathbb{M}_{\ell}$ | pairs of any memory events to the same loca-<br>tion in program order |  |

| read-read pairs                        | $\mathbb{R} 	imes \mathbb{R}$                | pairs of reads in program order                                       |  |

| read-read pairs to the same location   | $\mathbb{R}_{\ell} 	imes \mathbb{R}_{\ell}$  | pairs of reads from the same location in pro-<br>gram order           |  |

| read-write pairs                       | $\mathbb{R}\times\mathbb{W}$                 | read followed by write in program order                               |  |

| read-write pairs to the same location  | $\mathbb{R}_{\ell} \times \mathbb{W}_{\ell}$ | read followed by write to the same location in program order          |  |

| write-write pairs                      | $\mathbb{W}\times\mathbb{W}$                 | pairs of writes in program order                                      |  |

| write-write pairs to the same location | $\mathbb{W}_{\ell} \times \mathbb{W}_{\ell}$ | pairs of writes to the same location in pro-<br>gram order            |  |

| write-read pairs                       | $\mathbb{W}\times\mathbb{R}$                 | write followed by read in program order                               |  |

| write-read pairs to the same location  | $\mathbb{W}_{\ell} \times \mathbb{R}_{\ell}$ | write followed by read from the same location<br>in program order     |  |

(a) A Program (b) An Execution Witness

Figure 3.5: A Program and a Candidate Execution

## 3.2.1 Read-From Map

We write  $w \xrightarrow{\text{rf}} r$  to mean that r loads the value stored by w (so w and r must share the same location). In any execution, given a read r there exists a unique write w such that  $w \xrightarrow{\text{rf}} r$  (w can be an *init* store when r loads from the initial state). Thus,  $\xrightarrow{\text{rf}}$  must be well formed following the wf-rf predicate:

## Definition 14 (Well-Formed Read-From Map)

$$\mathsf{wf-rf}(\stackrel{\mathrm{rf}}{\to}) \triangleq \left( \stackrel{\mathrm{rf}}{\to} \subseteq \bigcup_{\ell} (\mathbb{W}_{\ell} \times \mathbb{R}_{\ell}) \right) \land \ (\forall r, \ \exists ! w. \ w \stackrel{\mathrm{rf}}{\to} r)$$

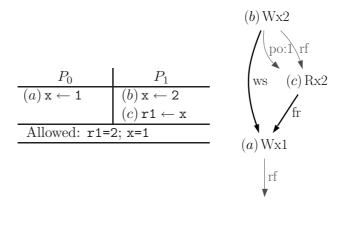

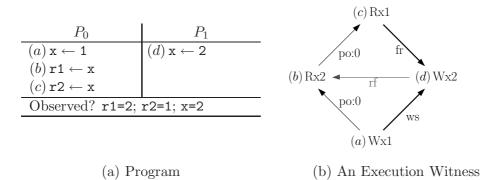

Consider the example given in Fig. 3.5(a). In the associated execution given in Fig. 3.5(b), the read (c) from x on  $P_1$  reads its value from the write (b) to x on  $P_1$ . Hence we have a  $\xrightarrow{\text{rf}}$  relation between them, depicted in the execution: (b)  $\xrightarrow{\text{rf}}$  (c).

## 3.2.2 Write Serialisation

We assume all values written to a given location  $\ell$  to be serialised, following a *coherence order*. This property is widely assumed by modern architectures. We define  $\xrightarrow{\text{ws}}$  as the union of the coherence orders for all memory locations, which must be well formed following the wf-ws predicate:

#### Definition 15 (Well-Formed Write Serialisation)

$$\mathsf{wf-ws}(\stackrel{\mathrm{ws}}{\to}) \triangleq \left( \stackrel{\mathrm{ws}}{\to} \subseteq \bigcup_{\ell} (\mathbb{W}_{\ell} \times \mathbb{W}_{\ell}) \right) \land \left( \forall \ell. \text{ total-order} \left( \stackrel{\mathrm{ws}}{\to}, (\mathbb{W}_{\ell} \times \mathbb{W}_{\ell}) \right) \right)$$

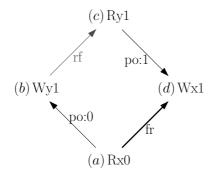

Figure 3.6:  $\xrightarrow{\text{fr}}$  Proceeds From  $\xrightarrow{\text{rf}}$  and  $\xrightarrow{\text{ws}}$

Consider the example given in Fig. 3.5(a). In the associated execution given in Fig. 3.5(b), the write (b) to x on  $P_1$  hits the memory before the write (a) to x on  $P_0$ . Hence we have a  $\xrightarrow{\text{ws}}$  relation between them, depicted in the execution:  $(b) \xrightarrow{\text{ws}} (a)$ .

As we shall see in Sec. 3.3.1, we will embed the write events in our global timeline according to the write serialisation.

#### 3.2.3 From-Read Map

We define the derived relation  $\stackrel{\text{fr}}{\rightarrow}[ABJ^+]$  which gathers all pairs of reads r and writes w such that r reads from a write that is before w in  $\stackrel{\text{ws}}{\rightarrow}$ , as depicted in Fig. 3.6. Intuitively, a read r is in  $\stackrel{\text{fr}}{\rightarrow}$  with a write w when r reads from a write that hit the memory before w did:

#### Definition 16 (From-Read Map)

$$r \xrightarrow{\text{fr}} w \triangleq \exists w' \cdot w' \xrightarrow{\text{rf}} r \wedge w' \xrightarrow{\text{ws}} w$$

Consider the example given in Fig. 3.5(a). In the associated execution given in Fig. 3.5(b), the write (b) to x on  $P_1$  hits the memory before the write (a) to x on  $P_0$ , *i.e.* (b)  $\xrightarrow{\text{ws}}$  (a). Moreover, the read (c) from x on  $P_1$  reads its value from the write (b) to x on  $P_1$ , *i.e.* (b)  $\xrightarrow{\text{rf}}$  (c). Hence we have a  $\xrightarrow{\text{fr}}$  relation between (c) and (a) (*i.e.* (c)  $\xrightarrow{\text{fr}}$  (a)) because (c) reads from a write which is older than (a) in the write serialisation.

As we shall see in Sec. 3.3.1, we will use the  $\xrightarrow{\text{fr}}$  relation to include the read events in our global timeline.

#### 3.2.4 All Together

Given a certain event structure E, we call the  $\stackrel{\text{rf}}{\rightarrow}$ ,  $\stackrel{\text{ws}}{\rightarrow}$  and  $\stackrel{\text{fr}}{\rightarrow}$  relations the *communication* relations, and we write  $\stackrel{\text{com}}{\rightarrow}$  for their union:

Definition 17 (Communication Relation)

$$\stackrel{\rm com}{\rightarrow} \stackrel{\Delta}{=} \stackrel{\rm rf}{\rightarrow} \bigcup \stackrel{\rm ws}{\rightarrow} \bigcup \stackrel{\rm fr}{\rightarrow}$$

We define an *execution witness* X associated with an event structure E as follows:

#### Definition 18 (Execution Witness)

$$X \triangleq (\stackrel{\mathrm{rf}}{\to}, \stackrel{\mathrm{ws}}{\to})$$

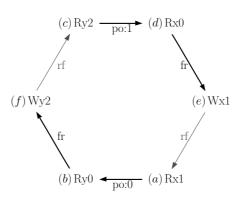

For example, we give in Fig. 3.2 an execution witness associated with the program of Fig. 3.1(a). The set of events is  $\{(a), (b), (c), (d)\}$ , the program order is  $(a) \xrightarrow{po} (b), (c) \xrightarrow{po} (d)$ . Since the initial state is implicitly a write preceding any other write to the same location in the write serialisation, the only communication arrows we have between the events of this execution are  $(b) \xrightarrow{fr} (c)$  and  $(d) \xrightarrow{fr} (a)$ .

The well-formedness predicate wf on execution witnesses is the conjunction of those for  $\stackrel{\text{ws}}{\rightarrow}$  and  $\stackrel{\text{rf}}{\rightarrow}$ . We write rf(X) (resp. ws(X), po(X)) to extract the  $\stackrel{\text{rf}}{\rightarrow}$  (resp.  $\stackrel{\text{ws}}{\rightarrow}$ ,  $\stackrel{\text{po}}{\rightarrow}$ ) relation from a given execution witness X. When X is clear from the context, we may write  $\stackrel{\text{rf}}{\rightarrow}$  instead of rf(X) for example.

#### Definition 19 (Well-Formed Execution Witness)

$wf(X) \triangleq wf-rf(rf(X)) \land wf-ws(ws(X))$

## **3.3** Global Happens-Before

We consider an execution to be valid when we can embed the memory events of this execution is a single global timeline. By global we mean that the memory events are the events relative to memory actions, in a way that every processor involved has to take them into account. Therefore, we do not consider the events relative to store buffers or caches, but rather we wait until these events hit the main memory. Thus, we focus on the history of the system from the main memory's point of view.

Hence, an execution witness is valid if the memory events can be embedded in an acyclic global happens-before relation  $\xrightarrow{\text{ghb}}$  (together with two auxiliary conditions detailed in Sec. 3.4). This order corresponds roughly to the vendor documentation concept of memory events being globally performed [pow09, DS90]: a write in  $\xrightarrow{\text{ghb}}$  represents the point in global time when this write becomes visible to all processors; whereas a read in  $\xrightarrow{\text{ghb}}$  represents the point in global time when the read takes place. We will formalise this notion later on, at Sec. 3.3.4.

In order to do so, we present first the choices as to which relations we include in  $\xrightarrow{\text{ghb}}$  (*i.e.* which we consider to be in global time). Thereby we define a class of models. In the following, we will call a relation *global* when it is included in  $\xrightarrow{\text{ghb}}$ . Intuitively, a relation is considered global if the participants of the system have to take it into account to build a valid execution.

Figure 3.7: Store Buffering

## 3.3.1 Globality

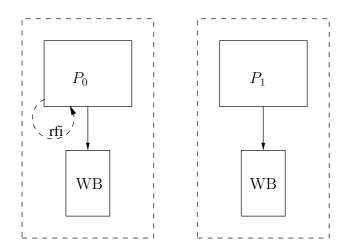

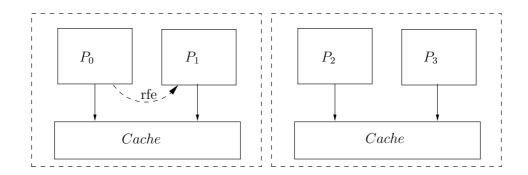

Writes are not necessarily globally performed at once. Some architectures allow store buffering (or read own writes early [AG95]): the processor issuing a given write can read its value before any other participant has access to it. Other architectures allow two processors sharing a cache to read a write issued by their neighbour w.r.t. the cache hierarchy before any other participant that does not share the same cache (a case of store atomicity relaxation, or read others' writes early [AG95]).

In our class of models,  $\xrightarrow{\text{ws}}$  is always included in  $\xrightarrow{\text{ghb}}$ . Indeed, the write serialisation for a given location  $\ell$  is by definition the order in which writes to  $\ell$  are globally performed.

Yet,  $\xrightarrow{\mathrm{rf}}$  is not necessarily included in  $\xrightarrow{\mathrm{ghb}}$ . Let us distinguish between internal (resp. external)  $\xrightarrow{\mathrm{rf}}$ , when the two events in  $\xrightarrow{\mathrm{rf}}$  are on the same (resp. distinct) processor(s), written  $\xrightarrow{\mathrm{rfi}}$  (resp.  $\xrightarrow{\mathrm{rfe}}$ ) :

#### Definition 20 (Internal and External Read-From Map)